1、PLL通过和VCO配合使用在通信系统中,可以实现输出信号频率对输入信号频率pfd时钟pll区别的自动跟踪,其特点是利用外部输入的参考信号控制环路内部振荡信号的频率和相位PLLPhase Locked Loop是指锁相环或者锁相环路,满足通信系统不同本振频率的需求,主要用于频率源模块中;赴青山的情侣名就是游绿水 这是最佳搭配,送给你,希望采纳哦;3 精准比较者PFD PFD持续比较输入信号的频率和相位 提供同步反馈,确保PLL系统的精准同步,是PLL实现频率锁定和相位同步的关键4 电流调节的电荷泵和LPF 电荷泵和LPF组成的系统处理PFD的输出信号 通过电荷转移调整VCO的频率,实现动态频率跟踪,保持输出频率与输入频率的完美同步锁相环的运作;II类 PLL鉴频鉴相器 PFDII类PLL通过引入鉴频鉴相器phasefrequency detector, PFD克服pfd时钟pll区别了I类PLL捕获范围低的问题PFD不仅作为鉴相器锁定环路的相位,还能作为鉴频器,通过调节VCO频率使输入和输出频率相等电荷泵 Charge Pumps电荷泵通过在特定时间周期内获取或泄放电流,克服了简单PLL的缺点Up;这个软件其实挺简单,就是设置PFD,电荷泵增益,主要是用来设计LPF,相噪估算的也挺准;PLL的核心操作涉及电荷泵,它根据PFD的比较结果产生电流,通过低通滤波器积分后,调节VCO的调谐电压这样,当两个PFD输入锁定到相同频率时,系统实现时钟净化对于需要生成更高频率的应用,如跳频或扩频跳频FHSS中的VCO,使用压控振荡器,其调谐范围比VCXO更宽这类PLL的关键性能参数包括相位噪声和频率。

2、PLL为一负回授系统,在回路中利用回授讯号,将输出端的讯号频率及相位,锁定在输入端参考讯号的频率及相位上锁相回路是一个实现相位锁定的控制系统,在锁相回路频率合成中,锁相回路具有稳频的功能,随著通讯卫星及量测仪器技术之发展,锁相回频率合成器已广泛用作高频讯号源PLL是由相位比较器回路。

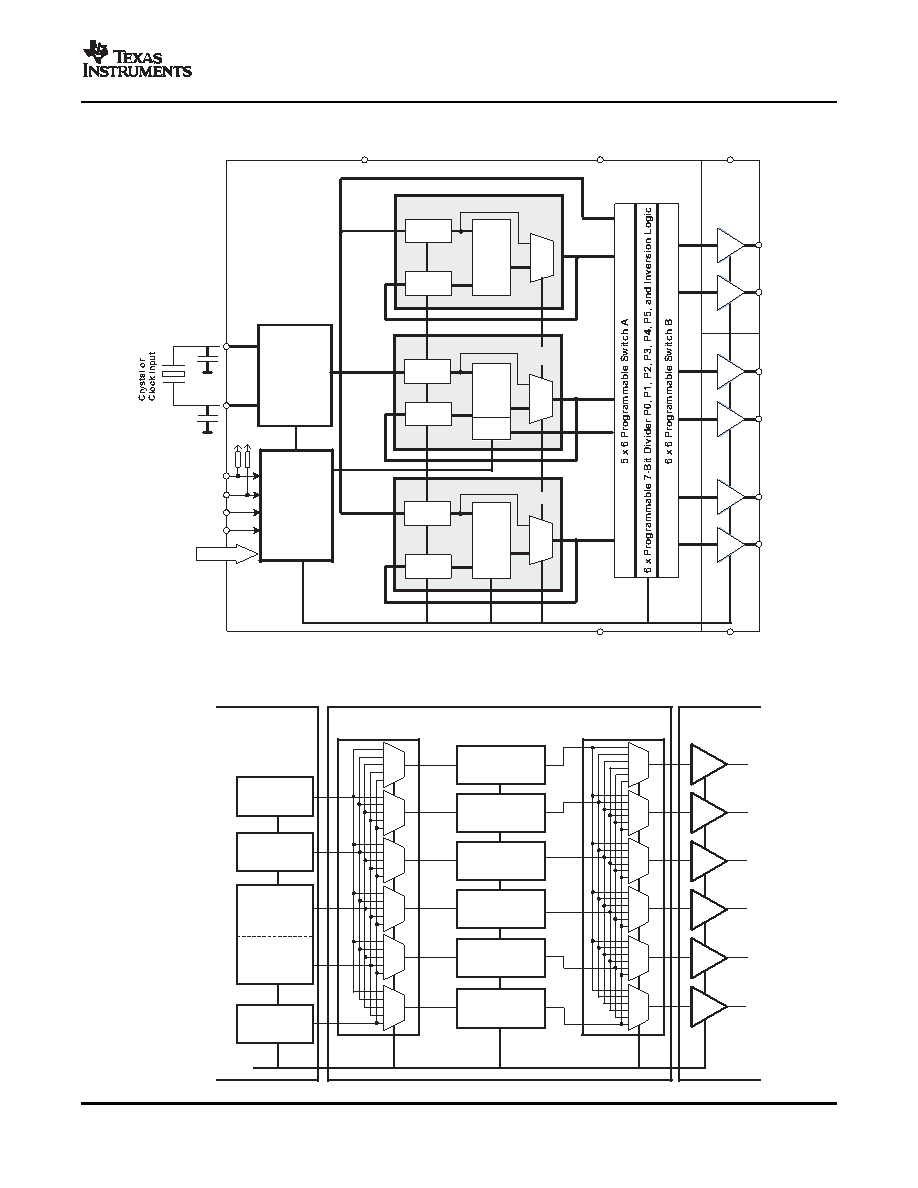

3、value for divider P + 2 The UPLL within the clock generator is the same as the MPLL in every aspectThe following sections describe the operation of the PLL, including the phase difference detector, the charge pump, the Voltage controlled oscillator VCO, and the loop filter;ADSB是什么?ADSBAutomatic Dependent Surveillance Broadcast,广播式自动相关监视是一套系统,或者说是一种技术手段通过飞机上的机载GPS等系统,获得飞机自身的位置信息,再通过飞机上的通信设备,将飞机自身的位置信息发送出来,地面人员可以利用通信设备,接收到飞机发送出来的这些信息,从而实现对;如果您使用的是华为平板,请观察您的平板故障现象,按照以下对应的方法进行排查1开机时平板黑屏,但是有铃声或振动 可能是屏幕问题,请提前备份好数据,微信等第三方应用需单独备份并携带相关购机凭证到附近的华为客户服务中心检修2开机时平板黑屏,无响应,或闪红灯,或亮屏后又立即关机;PLL是电子电路设计中的关键模块,其核心功能在于稳定信号的频率和相位,广泛应用于通信无线时钟生成频谱分析音频处理等多个领域本次课程采用TSMC 65nm工艺,不仅体现了高性能和可定制性,更让学习者亲身体验到真实流片项目的重要性与价值课程模块包括鉴频鉴相器PhaseFrequency Detector,PFD。

4、2PLL对频率的控制主要就是通过反馈回路上的DIV实现的,设置不同的系数就可以得到不同的输出频率了3锁相环会有一个技术指标叫锁定范围,如果输入和反馈的信号频率或者相位差超过这个阈值,那么锁相环就无法锁定和跟踪了失锁的判断很简单,就是输出频率相位很不稳定的乱跳同理如果已经锁定,那么;蛋白虫的养殖前景很一般,因为这个养殖业已经有很多年了,但是一直都没有发展起来,因为很多人接受不了这种方式补充蛋白;这种情况调电路的话主要是你的pfd增益不够,或者鉴相死区过大引起的可以先看下pfd鉴相死区多大,然后看下增益够不够,如果已经建模,可以代入到模型中仿真下;PLL的时钟输入 专用时钟输入管脚1÷n计数器 areset areset是高有效信号,复位所有的PLL计数器为初始值当该信号为高时,PLL复位该计数器,失锁一旦该信号再次变低时,锁定过程开始,PLL重新和输入参考时钟同步可以由内部逻辑或任意通用IO管脚驱动areset逻辑阵列3PFD 这个是输入信号 下面。

还没有评论,来说两句吧...