高速串行收发器的作用在FPGA中实现10G以太网接口时,高速串行收发器起着至关重要的作用这些收发器通过SerDes技术实现Gbps速率的通信,从而支持10G以太网接口的高速数据传输常见的GT收发器类型包括GTXGTH和GTY等。

提供两套 Vivado 工程源码,以适应不同的应用场景GTX 的核心原理基于串行数据的高速传输与处理它通过 PMA物理媒介适配层和 PCS物理编码子层来实现数据的编码与解码,支持多种串行传输接口或协议,如 PCIE万兆网 XUAIOC48SDI 等GTX 的基本结构由四个通道Channel和一个 QPLL。

TicWatch还提供gtxgth的区别了GTAGTHGTK和GTX等系列,以及手环版,这些产品注重基础功能与轻便性其中,GTH2和GTA凭借方圆屏幕与全面功能脱颖而出,GTH2提供方正屏设计和全面的健康监测,支持语音交互,防水性能适合日常使用GTH以轻便与防水著称,适合手腕较小的运动者GTA则以圆润设计和长续航赢得传统手表爱好者。

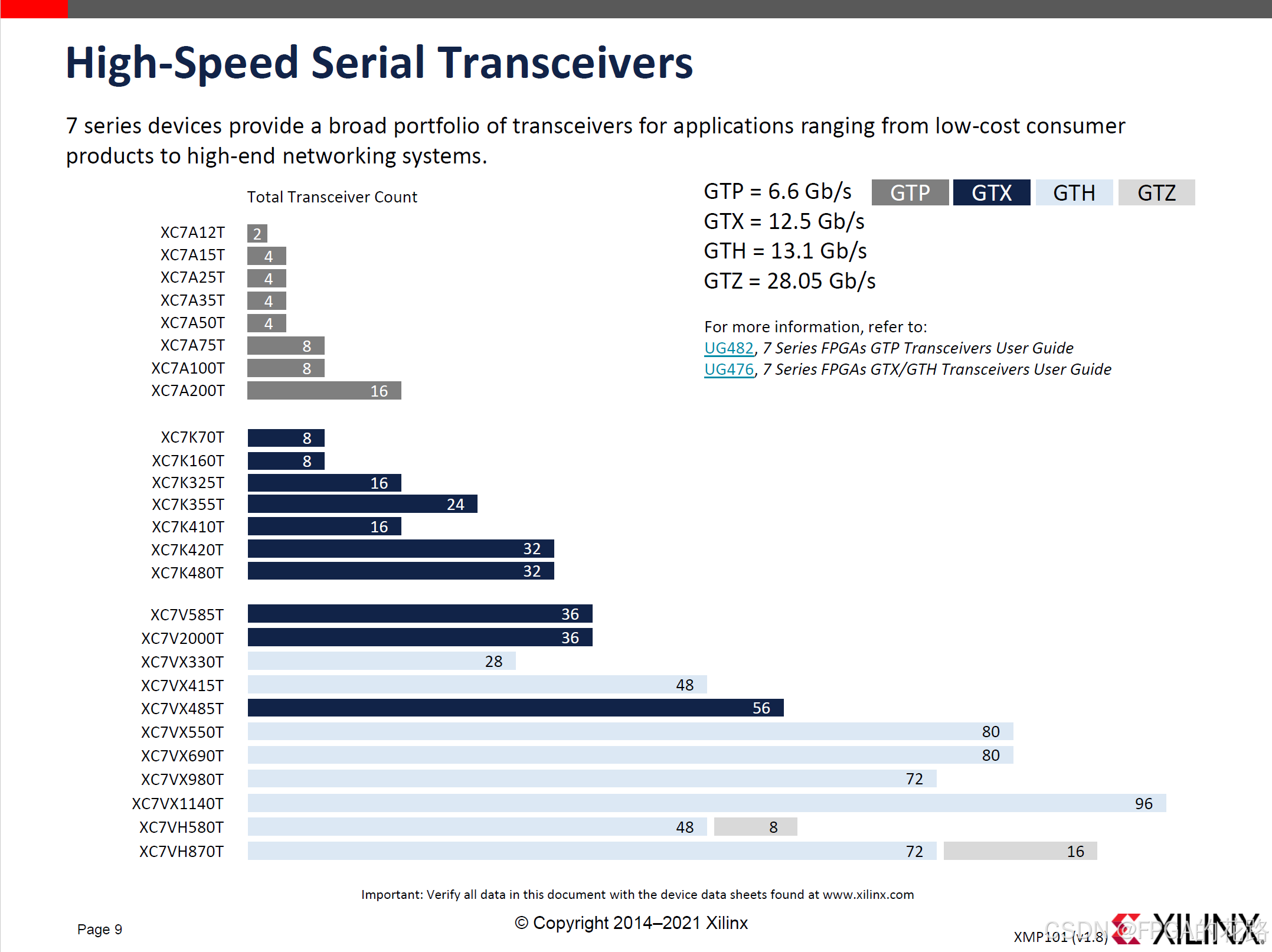

serdes = serial and deserial吧,就是组串器与解串器,也就是通用的高速IOGTX,GTP,GTH等都是SERDES,只是速率不一样,XILINX叫其不同的名字方便区分。

UltraScale GTH相比于GTH,线速率更高,支持协议类型更多,功耗更低,带宽更高本文使用Xilinx的Kirtex UltraScale+系列的xcku5pffvb6761i型号FPGA的UltraScale GTY资源做板对板视频传输实验视频源有两种,一种是使用笔记本电脑模拟HDMI视频,ADV7611芯片将输入的HDMI视频解码为GRB后供FPGA使用视频。

GT Transceiver的回环模式是一种关键的配置,它通过数据流的反向传输进行错误检测这种模式在开发和故障排查中都扮演着重要角色,支持两种主要的回环测试类型应用流量模式和伪随机比特序列每个GTXGTH收发器内置了PRBS发生器和检查器,为测试提供了便利在具体操作中,回环测试涉及几个关键参数,如RX_。

首先,device clock频率由产品决定,其生成途径涉及PLL等时钟路径对于FPGA,其GTXGTH结构提供了两个reference clock选项,通过配置内部PLL与时钟路径实现支持不同serdes data rate的RXTX因此,device clock频率取决于FPGA配置,由FPGA设计工程师指定需求类似地,ADCDAC的device clock需参照产品说明书。

应用流量模式模拟实际数据传输场景,用于测试收发器在实际应用中的性能伪随机比特序列利用GTXGTH收发器内置的PRBS发生器和检查器,生成并检测伪随机比特序列,以验证数据传输的完整性和准确性关键参数RX_XCLK_SEL用于选择驱动RX并行时钟域的时钟源在近端PCS环回时,通常选择RXREC,以利用RX。

GTxGiga bits Transceiver,FPGA的收发器,66GbsGTP,125GbsGTX,131GbsGTH,2805GbsGTZUltraScale中的GTH线速率可达 16375 Gbs,GTY 305 GbsUltraScale+ GTY 3275 GbsHP IOHighperformance IO with support for IO voltage from 12V to。

提供完整的工程源码与技术支持,适用于学生毕业设计工程师项目开发,尤其在医疗军工等数字成像与图像传输领域工程代码已通过编译验证,并附有演示视频,便于直接移植使用已有SDI编解码方案包括基于GTXGTH的解码GS2971GS2972等芯片的SDI收发工程,以及PCIE通信方案,涉及基于RIFFA与XDMA的实现总体。

幽默一点说的话N种,每次每批都不一样的颜色,呵呵一般南方北方说法不一致,gtxgth的区别我是比较准确的镀种为镀镍白色,镀铜黄色,镀锌青白色,镀铬闪白经过化学氧化后会有白,银白,深银白古银古银黑黑南方一般成为浅克呖深克哩古铜深古铜红古铜青古铜。

GT资源是Xilinx系列FPGA的重要卖点,也是做高速接口的基础,不管是PCIESATAMAC等,都需要用到GT资源来做数据高速串化和解串处理,Xilinx不同的FPGA系列拥有不同的GT资源类型,低端的A7由GTP,K7有GTX,V7有GTH,更高端的U+系列还有GTY等,他们的速度越来越高,应用场景也越来越高端本文使用Xilinx的Zynq7100 FPGA的GTX。

作者主页有FPGA GT高速接口专栏,包含GTPGTXGTHGTY等GT资源的视频传输例程和PCIE传输例程,适用于不同FPGA系列开发板搭建设计思路基于FPGA硬件架构,详细描述了HSSTLP接口与OV5640摄像头的集成应用视频数据封装与解码模块通过状态机实现,确保数据在HSSTLP接口传输过程中的正确性按键选择功能根据。

GT Transceiver TX模块中的核心时钟机制在设计和操作中起着关键作用首先,让我们关注两个重要的时钟源TXUSRCLK和TXUSRCLK2TXUSRCLK是GTXGTH transceiver内部PCS逻辑的驱动时钟,其速率由GTXE2_CHANNELGTHE2_CHANNEL源的数据通路宽度和TX线速率决定计算所需速率的公式揭示了其精准性的重要性相比。

放在近端比较好一些,对于Serdes信号来说,加AC耦合电容主要是考虑近端和远端串扰,按照串扰的原理,对于理想的带状线stripline来说,近端串扰相互加强,远端串扰相互抵消,因此AC耦合电容加在靠近发送端会更有效当然对于实际的PCB layout,走线不可能是理想带状线,因为要经过top层走线过孔等非。

还没有评论,来说两句吧...